由 Jeff Zopff | 3 月 9, 2015 | Blog @zh-hans

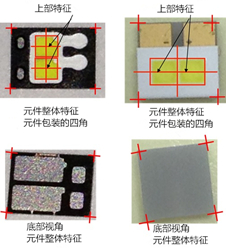

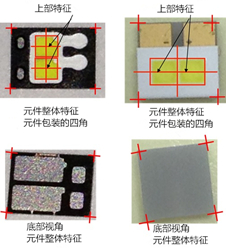

[section background_repeat=”repeat” background_position=”center top” background_attachment=”static” background_scroll=”none”] 2015年3月9日 – 环球仪器专有的上部校准工艺(Topside Alignment Placement – TAP)以元件上部特征作为参考,可实现高精度贴装。...

由 Jeff Zopff | 2 月 6, 2015 | Blog @zh-hans

[section background_repeat=”repeat” background_position=”center top” background_attachment=”static” background_scroll=”none”] 2015年2月6日 –...

由 Jeff Zopff | 1 月 7, 2015 | Blog @zh-hans

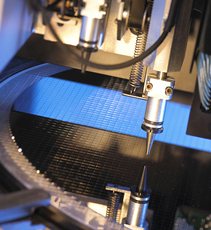

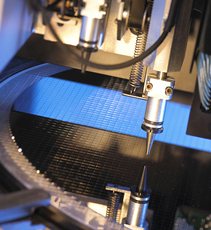

2015年1月6日 – 试想,如果想将主动元件WLCSPs,uBGAs与被动元件SMDs借助锡膏和助焊剂相互连接在电路基片上,则必须使用诸多设备、经过一系列流程、花费相当多时间才能达成。...

由 Jeff Zopff | 12 月 3, 2014 | Blog @zh-hans

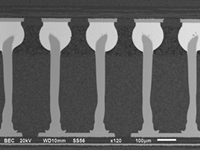

2014年12月3日 – 一直以来,半导体封装产业往往根据封装对象来决定所使用的设备,裸晶(Bare Die)有其专有的封装形式和工艺,倒装芯片(Flip Chip)也有其专有的贴装形式和工艺。新封装形式的功能,性能,微型化程度以及材料成本是否低廉,对产品生命周期中的关键环节–上市时间–起着至关重要的作用;它们也成为当前半导体封装产业所面临的最大挑战。设备的封装区域越大,在每一工艺环节处理的元件越多,生产成本才能降下来。封装技术 —...

由 Jeff Zopff | 8 月 4, 2014 | Blog @zh-hans

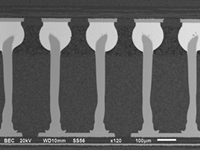

August 1, 2014 -元件堆叠(PoP)技术从第一代发展至今已有5年历史,其主要目的是合并内存芯片和专用集成芯片,同时缩小元件封装的尺寸。这种3D方式的装配技术越来越多地被要求在生产工艺中实现。 我们在此将会讨论影响封装尺寸缩小的主要因素,如何实现主动和被动元件成为基板的一部分,进而降低封装的高度。所有的最经济,最先进的封装技术我们都会讨论到。 移动终端的发展趋势 移动终端的趋势为单一设备多样功能 需要极高的计算机性能和极低的能耗 小型化,高性能:细间距/小锡球;高密度/密间距...