August 1, 2014 -元件堆叠(PoP)技术从第一代发展至今已有5年历史,其主要目的是合并内存芯片和专用集成芯片,同时缩小元件封装的尺寸。这种3D方式的装配技术越来越多地被要求在生产工艺中实现。

我们在此将会讨论影响封装尺寸缩小的主要因素,如何实现主动和被动元件成为基板的一部分,进而降低封装的高度。所有的最经济,最先进的封装技术我们都会讨论到。

移动终端的发展趋势

- 移动终端的趋势为单一设备多样功能

- 需要极高的计算机性能和极低的能耗

- 小型化,高性能:细间距/小锡球;高密度/密间距

- 由于芯片的小型化越来越难实现,所以对元件堆叠应用要求越来越高,进而出现了2.5D&3D的堆叠工艺:制造商的新挑战:新物料,工艺复杂,单一平台多种工艺融合;更薄的晶片和基板

为什么需要元件堆叠

- 体积小型化(更小更轻)

- 更好的电子性能,更低的能耗

- 存储模块可以单独测试

- 仅已知的合格封装才被使用

- 终端客户控制物流(存储模块可从逻辑芯片上移除)

- 各种规格的存储模块均可使用

- 逻辑芯片供应商不需要处理存储模块

- 主要应用:无线技术(手机,平板,GPS,PDA);数码相机;宽频模块;游戏及其他移动应用

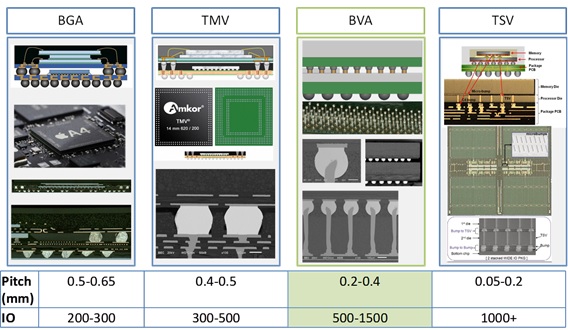

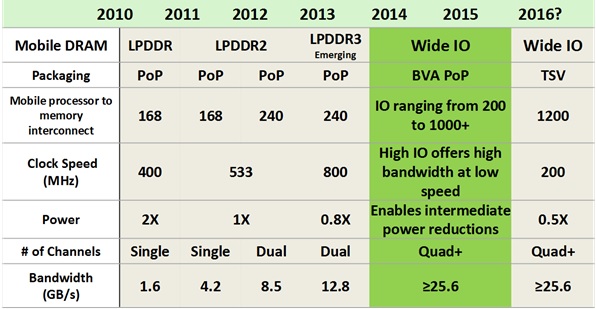

处理器+存储堆叠方案

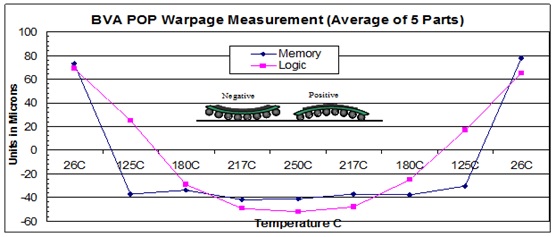

相对于TSV,BVA的优势在于可以利用当前现有的封装物料,支撑和设备。

BVA PoP:不依赖TSV即可实现对广域通信的支持

- 广域通信在当前存储级别上有了数量级的提升

- 带TSV的广域通信将在接下来的数年中被淘汰

- BVA(阵列式结合)将在当前的元件堆叠基础上实现广域通信

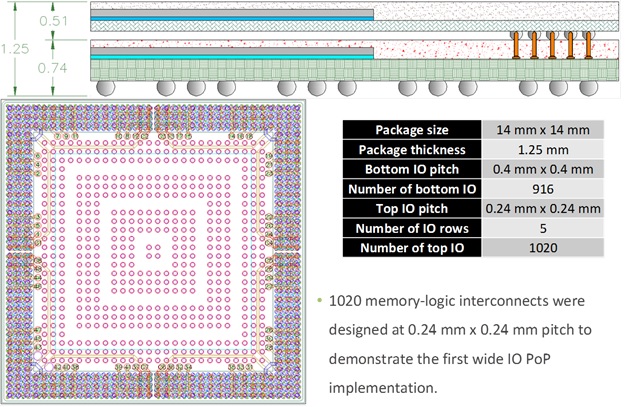

BVA封装

该广域通讯的案例是在0.24mm*0.24mm的范围内实现1020组逻辑通讯。

元件堆叠的参数

- 锡球间距–240um 到650um

- 锡球材料– 104,,305, 405,SAC,锡银合金,锡铅合金等等

- 锡球尺寸–通常为175um到390um

- 锡球和BVA的共面性

- 锡球和BVA的焊接性

- 封装温度测试:JEDEC Level 1-6(Level 3测试):元件暴露多少时间后需要烘烤

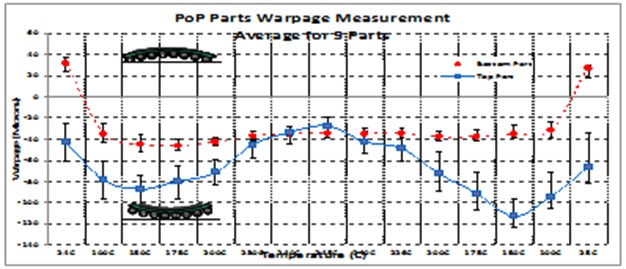

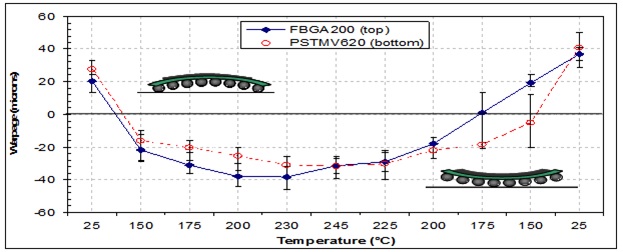

元件堆叠的翘曲

第一代PoP

- 整体量级< 90um

- 匹配不佳

- JEIDA 标准7306:0.5mm间距;最大翘曲110 microns

第二代PoP

- 整体量级< 50um

- 绝佳匹配

- JEIDA标准 7306:0.5mm间距;最大翘曲110 microns

下一代PoP

- 整体量级<100um

- 绝佳匹配

BVA装配工艺优化

装配工艺步骤,可靠性&质量分析:

- 线路板设计和参数设定

- 丝网印刷工艺参数

- 丝网设计&参数设定

- 丝印结果

- 助焊剂应用

- 装配= PCB上堆叠(成品)和预先堆叠

- 回流焊参数设定

- 可靠性增强

- 可靠性测试

- 可靠性结果

*工艺优化在环球仪器的先进工艺实验室完成

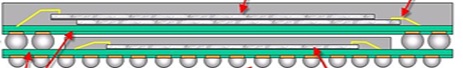

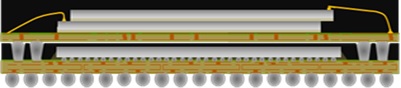

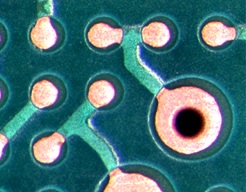

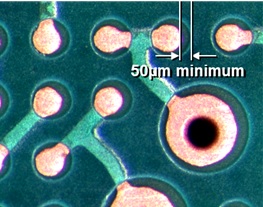

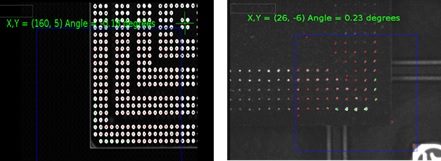

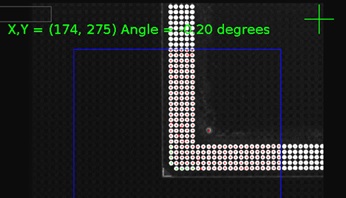

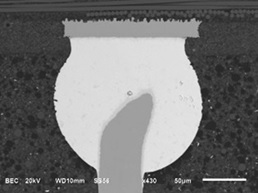

左:PCB图例-PoP通孔

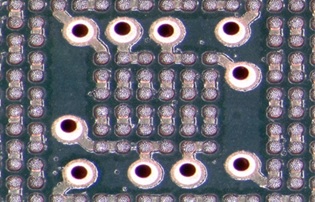

中: BVA PoP图例 – 剖面图

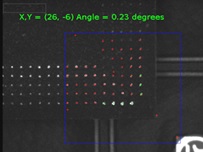

右: 底层PoP元件识别影像

PCB设计和参数设定

900+I/O(14mm)

- 阻焊层(SMD)或非阻焊层(NSMD):SMD 用于保证焊盘尺寸的一致性,NSMD利于焊盘的形成,等等

- 焊盘通孔或顶层链接(狗骨设计),如果用焊盘通孔设计,焊锡则应该填充满至焊盘

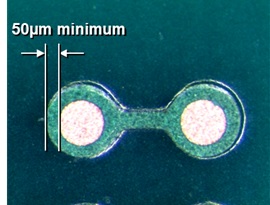

- 焊盘尺寸应该约等于间距的50%到57%

- SMD应该至少改过或截断NSMD至50um

- 附着焊盘完成:镍/金;抗氧化铜;浸入式锡;浸入式银

- 基准点:如果用SMD焊盘,SMD基准点应该设计为等同于贴片焊盘

左: SMD-阻焊层

右:NSMD-非阻焊层

丝网印刷工艺参数

- 主要的印刷工艺参数:刮刀材质:电成型,不锈钢等等;刮刀角度:推荐60度;刮刀压力:因产品而异;印刷速度:依赖于网孔尺寸和锡膏用量来定义;分离速度;印刷间隙:有或无;PCB支撑

- 小孔径的印刷工艺控制:印刷时间的控制—干燥时间和底部脱离时间

- 新的丝网印刷技术:Ultra Sonic刮刀

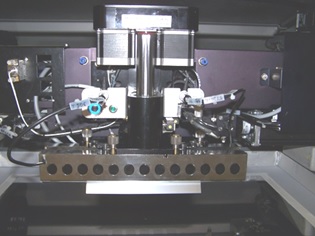

左: Ultra Sonic刮刀

右: 0.3mm间距PoP

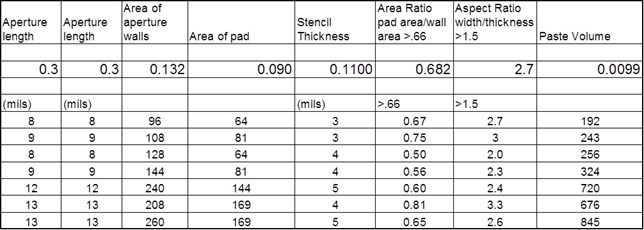

丝网设计和参数

- PoP丝网设计:丝网厚度:决定于间距和应用元件(大部分采用75um到125um);开孔形状,推荐用圆角方形;开孔尺寸,决定于间距和翘曲度,近似于间距的64%;面积比,可以用公式自动计算,推荐值为>0.66

- 丝网技术:激光切割;电成型;纳米涂层

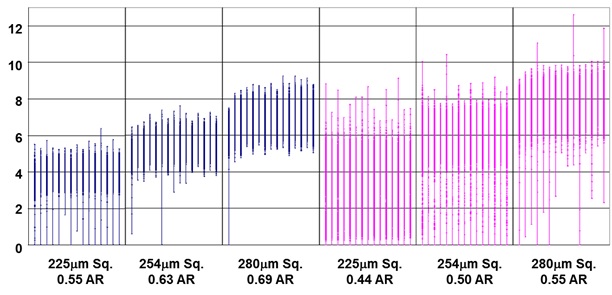

丝网参数表

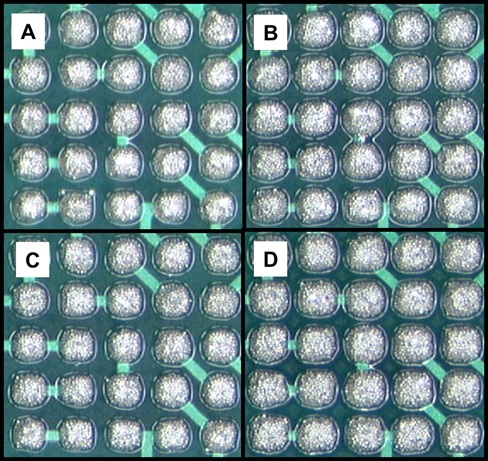

丝网印刷结果0.4mm间距

- 每组测试印刷15,期间没有清洁丝网

- 每条线代表基板上的所有印刷店(15种元件/9300个锡膏点)

- DEK Galaxy印刷机,foil-less夹具,真空支撑,60°,金属刮刀, V=30mm/s,P=4.6kg,分离速度=20mm/sec

A: 127um stencil, 254um apertures, oo much variability, lowest area ration

B: 127um stencil, 280um aperture, bridging risk

C: 101.6um stencil, 254um apertures, robust process

D: 101.6um stencil, 280um apertures, bridging risk

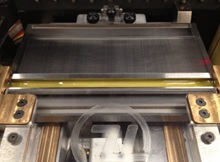

助焊剂应用

- 主要的助焊剂变量:粘度和流动性;粘性;类型(免洗,水溶性);回流后固化比例;无卤素;和其他材料兼容:印刷锡膏,底部填充等等

- 薄膜涂覆装置:线性驱动保持厚度的一致性;对不同粘度助焊剂的支持(小于200到大于900厘泊);多个仪器或逐个浸蘸;快速分解工具,容易清洗;凹槽设计保证浸蘸高度的一致性;基于压力浸蘸;基于压力反馈系统确保浸蘸的品质

左: 承载助焊剂的LTFA图例

中: LTFA图例

右:PoP制程图解

BVA 堆叠装配

- 两种类型的PoP装配:在PCB上堆叠;预先堆叠

左:在PCB上堆叠

右: 预先堆叠

装配工艺流程

- 丝网印刷锡膏(标准流程)

- 贴装流程:传板到设备中夹紧;设备检查定位点;吸取元件,检查四个边角的部分锡球,然后以100克到150克的压力贴装;检查BVA元件顶部的焊盘;吸取存储芯片,进行视觉检查,浸蘸前确认元件;在助焊剂中浸蘸存储芯片;检查边角的锡球,以30可的压力贴装;回流焊(标准流程)

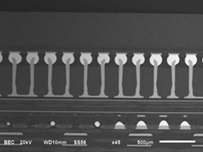

Left: Logic Balls (bottom side)

Middle: Logic Pins (top side)

Right: Memory Balls (bottom side)

- GenesisSC平台:一体化平台:硅/SMT,高精度/高速度装配;高精度:(±10um,<3um重复精度); 双横梁或单横梁,单头多个吸嘴;极宽范围的晶片和元件类型尺寸;支持各种类型的基板;支持各种送料方式;低维护,高性能;对锡球或逻辑焊盘的影像识别;支持元件堆叠(PoP):贴装前后的定位和贴装顺序的控制;低压力的控制

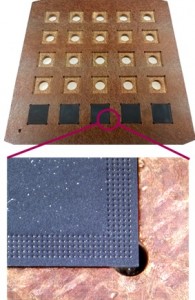

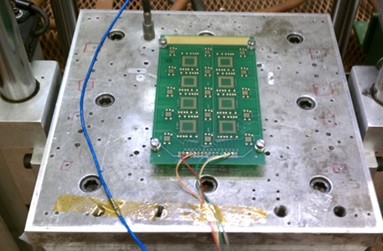

- 载具设计

- 装配过程中对顶层元件锡球的保护(避免对锡球的挤压)

- 载具材料:耐高温电木等等(防静电且易切割)

- 利用逻辑焊盘定位(每次贴装前)

- 对装配柔性的支持,一直薄膜涂覆装置(LTFA)可以支持多个装配需要

- 装配结束:因为有回流焊流程,故需要考虑存储环境对温度的去除(使用干燥剂&真空密封或烘烤)

- 需要新的托盘以承载堆叠后的元件(原先的托盘已经不再适用)

- 预堆叠流程至此全部结束

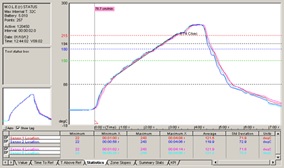

主要回流参数

- 空气或氮气

- 单一或二级温度曲线

- 焊接激活时间

- 峰值温度

- 液化的时间(减少虚焊)

- 为两种不同的焊料优化温度曲线?

- 绝大多数的PoP封装有相对低的热能值

回流曲线和回流后切片图像

可靠性增强

- 可靠性应用:没有后期焊接的可靠性增强;底部填充;边缘填充;筑坝填充

- 助焊剂残留 & 底部填充的兼容性

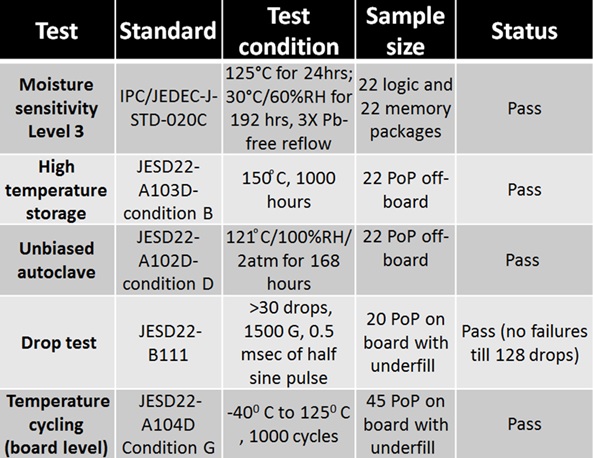

可靠性试验

- 热循环或冲击

- 弯曲

- 掉落

- 振动

- 高压

- 高温

- 液体

- 温度

冲击测试

可靠性测试结果

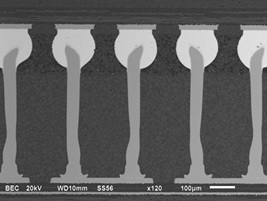

装配质量分析

- X-ray (2D & 3D)

- 切片分析

- 超声显微镜C-SAM(底部填充)

- 分段切割或红墨水试验

左: 切片图像

右: X-ray结果

业界对在更薄更小尺寸的芯片上实现高性能存储和高频率通讯的需求增长迅速。此类需求主要来自于平板电脑,智能手机和其他移动终端。这些设备被寄予越来越高的期望值。这些需求已经存在,相关的装配方案,工艺制程和物料必须早做准备以供需求。基于以上的介绍,一个可行的解决方案已经就绪。